# INSTITUT FÜR KOMMUNIKATIONSNETZE UND RECHNERSYSTEME

Prof. Dr.-Ing. Andreas Kirstädter

#### **Copyright Notice**

© 1981 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder.

Institute of Communication Networks and Computer Engineering

University of Stuttgart

Pfaffenwaldring 47, D-70569 Stuttgart, Germany

Phone: ++49-711-685-68026, Fax: ++49-711-685-67983

Email: mail@ikr.uni-stuttgart.de, http://www.ikr.uni-stuttgart.de

### Design of Economic PCM Arrays with a Prescribed Grade of Service

KLAUS ROTHMAIER AND REINHARD SCHELLER

Abstract—This paper deals with the design of economically structured PCM switching arrays for traffic distribution. The presented switching arrays are symmetrically structured, and have one up to six stages and use different combinations of time stages T and space stages S, respectively. It is shown how such arrays can be designed for a required grade of service having a prescribed number of terminations and a prescribed carried traffic per time slot. Their relative costs per termination equal to that per time slot are calculated. These are costs for the gates and costs for memory bits, i.e., speech memories and all control memories.

All presented PCM switching arrays are mapped into the corresponding space division multiplex (SDM) arrays. This allows a simple comparison with SDM link systems and an easy calculation of the point-to-point loss.

The paper concludes comparing the traffic behavior and costs of the various PCM switching arrays. Finally, new "PCM charts" are developed as useful means for the design of economic PCM switching arrays.

A second paper of this congress [14] compares traffic equivalent PCM and SDM switching arrays, respectively, with regard to their economic design, their traffic behavior, and their costs per termination.

#### I. INTRODUCTION

$\mathbf{D}$ UE to the decreasing costs of digital techniques, PCM switching becomes more and more an economic alternative to space division multiplex switching. Therefore, the aim of this paper is to give a systematic survey of suitable switching arrays using different types and sequences of stages within the array, namely time stages T and space stages S.

#### II. ELEMENTS OF A PCM SWITCHING ARRAY

#### A. The Space Stage

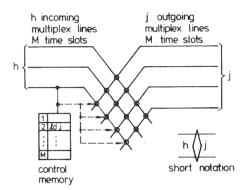

A space stage is composed of space switches (SS) consisting of matrices for time-multiplex lines (ML). Each switching matrix has h incoming and j outgoing ML's, having M time slots each. The number of outgoing ML's may be greater or less than the number of incoming ones.

The space stage only allows the coincident switching of time slots (TS) from each incoming ML to each outgoing ML. Switching is performed by logical gates, forming the crosspoints of the matrices. They are controlled by control memories. The cheapest realization is achieved if a control memory controls the gates of an incoming ML, if h < j. A control mem-

Paper approved by the Editor for Communication Switching of the IEEE Communications Society for publication after presentation at the 9th International Teletraffic Congress, Torremolinos, Spain, October 1979. Manuscript received October 13, 1980.

The authors are with the Institute of Switching and Data Technics, University of Stuttgart, Germany.

Fig. 1. Space switch.

ory has as many storage places as there are TS on the ML; each storage place needs [ldj] bits, where [] means the next greater integer value. To simplify the figures, a short notation for the SS is introduced, as shown in Fig. 1.

#### B. The Time Stage

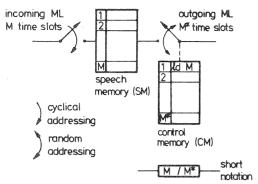

A time stage is composed of a number of time slot interchanges (TSI), consisting of speech memories and control memories.

A TSI allows the switching of each of the M time slots of the incoming ML's to each of the  $M^*$  time-slots of the outgoing ML's.  $M^*$  may be greater or less than M. Time slot interchanging is performed by the speech memory and the respective control memory. The control memory controls either writing into the speech memory or reading out from it. This function of random addressing is depicted in Fig. 2 by a double arrow. Reading or writing on the other side of the speech memory is done cyclically according to the time-slot counter.

The cheapest realization is achieved if the control memory controls that side of the speech memory where the number of time slots is greater.

To simplify the figures, a short notation for the TSI's is introduced, as shown in Fig. 2.

#### III. SWITCHING MODE AND ARRAY STRUCTURE

PCM switching is always four-wire equivalent, i.e., a PCM highway consists always of two multiplex lines (ML), one for each speech direction. Therefore, two time slots, one in each multiplex line, have to be provided for one speech connection.

The structure of a PCM switching array depends on the decision which of the two following switching modes should

Fig. 2. Time-slot interchange.

- separated switching, or

- combined switching.

#### A. Separated Switching

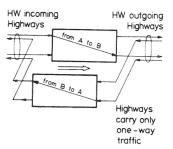

Separated switching (SSW) means that only connections from incoming highways to outgoing highways (from left to right) can be established. This leads to an array structure where *two* identical, but separated, arrays for the two speech directions have to be provided (see Fig. 3).

On the left-hand side of the two identical arrays all incoming highways, carrying only one-way traffic, terminate each speech direction (ML) on an array of its own. The same holds for the outgoing highways terminating on the right-hand side. If the two paths for the two speech directions in both arrays are chosen identically, it is sufficient to provide control memories only for one network; the other one can also be controlled by these memories.

This corresponds exactly to the unidirectional operation mode of many SDM link systems for traffic distribution.

#### B. Combined Switching

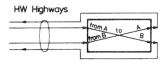

Combined switching (CSW) means that connections between all highways connected to the (one and only) array can be established; the highways may carry two-way traffic as well as one-way traffic.

The incoming speech directions of all highways terminate on the left-hand side of the array, the outgoing speech directions on the right-hand side (see Fig. 4). For each speech connection one has, therefore, to establish, in any case, two paths through the same combined switching array.

The manner how these two paths are allocated within the array has a remarkable influence on the costs. Suitable path allocation principles will be presented in the following chapter.

#### C. Path Allocation Principles for Combined Switching

Combined switching allows various path allocation principles to be applied in order to save control memories for gates as well as for speech memories. If the two paths of one speech connection (from  $A \rightarrow B$  and  $B \rightarrow A$ ) are switched symmetrically to the median vertical line, the control memories on the left-hand side can control the elements on the right-hand side, too.

It is necessary for all path allocation principles to have symmetrically structured PCM switching arrays, i.e., the types

Fig. 3. Separated switching mode.

Fig. 4. Combined switching mode.

and the numbers of stages have to be identical on both sides of the median vertical line.

This prerequisite holds for all investigations and switching arrays discussed in the following.

Two different principles are possible:

- the symmetrical path allocation, and

- the quasi-symmetrical path allocation.

The implementation of these principles varies, depending on the type of the first and the last stage of the switching array (T or S stage).

1) Path Allocation within  $T\cdots T$  Arrays. Symmetrical path allocation means that, in addition to the symmetrical switching, both paths of one connection of likewise numbered time slots are used between the first and the last T stage. Symmetrical path allocation has the restriction that connections between speech paths within the same highway cannot be established. Quasi-symmetrical path allocation, however, allows such connections.

For this purpose the two speech paths of one connection use an even/odd time-slot relation instead of likewise numbered TS [22].

Both allocation principles allow saving half of the control memories, if the number of stages is even; if not, control memories can be saved for all stages except for the middle

2) Path Allocation within  $S \cdots S$  Arrays. Symmetrical path allocation means that the two speech directions of one connection lead symmetrically over the same time-slot interchange in the middle T stage. Quasi-symmetrical path allocation differs, concerning the paths in the middle T stage. Now, these two paths do not lead through the same TSI; instead they lead through two related TSI's, which can be controlled by one control memory. Thus, half of the control memories of the middle stage can be saved as well.

For switching within the STSTS and STSSTS array, having no middle T stage, quasi-symmetrical path allocation is applied between the two T stages as described above.

#### IV. INVESTIGATED PCM ARRAYS

With T stages and S stages, a great variety of PCM switching arrays can be designed. Among all these arrays, only a few are symmetrically structured, i.e., the types and numbers of

stages on the left- and right-hand side of the median vertical line are identical. Only these symmetrical arrays allow savings in control memories, if a path allocation principle for combined switching is implemented. Arrays consisting only of space stages, will not be regarded as they have a very poor traffic behavior. Furthermore, systems with consecutive time stages are not considered, because they do not improve the traffic efficiency.

Thus, the one- to six-stage arrays described in the following remain the only arrays to fulfill the prerequisites. For each array design, formulas are given which are derived in a related paper of this ITC [14]. These formulas allow the building of economic PCM switching arrays. Furthermore, the mapping of PCM arrays into equivalent SDM arrays is presented using some examples. Mapping is advantageous in order to calculate the grade of service of the PCM switching arrays.

As in SDM arrays and in PCM arrays, an expansion in the first stage is possible to obtain a desired probability of loss. The realization of this expansion will be discussed in the following chapter.

#### A. Expansion of PCM Switching Arrays

It is known from SDM arrays that the loss probability is influenced by an expansion in the first stage and a corresponding concentration in the last stage; all multiples in the intermediate stages switch 1:1. This expansion leads to different realizations in PCM switching arrays depending on the type of the first and the last stage (S or T).

If both are T stages, expansion can be performed by increasing the number of time slots within the PCM array. This is, however, only possible up to a maximum clock frequency which is assumed to be about 8 MHz, for the time being. This clock frequency allows one ML to carry 120/128 TS if the voice samples are transmitted in serial and 960/1024 TS if parallel transmitting is applied. If the first and the last stage are S stages, expansion means to increase the number of outgoing ML's per SS in the first stage (cf. Fig. 1).

This is exactly the same method as that in SDM arrays.

The following assumptions hold for all presented PCM arrays:

- the PCM switching arrays are symmetrically structured and have as many incoming ML's as outgoing ones;

- expansion is always performed in the first stage, concentration in the last stage; all intermediate stages switch 1:1;

- the maximum clock frequency for switching is assumed to be 8.192 MHZ.

From this it follows:

- serial transmitting allows one ML to carry 120/128 TS;

- parallel transmitting allows one ML to carry 960/1024 TS.

#### B. One Stage Switching Array: The T-Stage

The T stage is only one time-slot interchange, consisting of a speech memory and a control memory (cf. Fig. 5). To allow switching between more than one PCM highway a certain number of them has to be multiplexed before switching into one ML; a maximum of 960/1024 TS per ML can be achieved; this corresponds to 32 PCM 30/32 systems. The T stage is strictly nonblocking.

Fig. 5. The time stage.

As it is known, this way of "T stage switching" is economic, at least up to 960/1024 terminations. If more than 960/1024 terminations (or TS, respectively) have to be switched the costs increase remarkably. A correct cost comparison with multistage PCM arrays seems to be very difficult and therefore has not been performed.

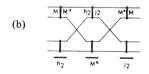

#### C. Three Stage Switching Arrays

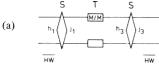

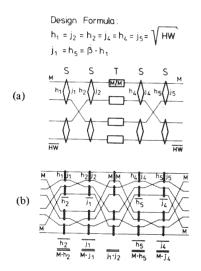

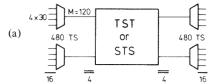

1) The STS Array: Fig. 6(a) shows the PCM array and Fig. 6(b) its mapped array. The mapping rules are as follows.

One time-slot interchange of the T stage becomes one multiple with M inlets and M outlets; the ML's on the left-and right-hand side of the TSI carry the same number of time slots

A space switch becomes a column of M multiples, each having  $h_1$  inlets and  $j_1$  outlets; and  $j_1$  has to be chosen such that the desired probability of loss is achieved. An expansion factor  $\beta$  is introduced which holds  $\beta = j_1/h_1$ .

The mapping of the incoming and outgoing ML's, connected to the first and last stage, respectively, is such that the M time slots of each ML terminate at M different multiples.

From this it follows that different marking methods can be applied:

- point-to-point marking, PPL calculation [9]

- point-to-point marking with multiple marking attempts, PPLM calculation [13]

- point-to-group marking, CLIGS calculation [1], [2].

The latter two marking methods are possible, as one trunk group, i.e., one PCM multiplex line can be reached via M different multiples of the last stage. It is well known that point-to-group marking leads to the lowest probability of loss, but requires the maximum time for path searching.

It is possible to make this array strictly nonblocking, if  $j_1$  is chosen to  $(2h_1 - 1)$  [5].

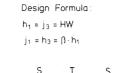

2) The TST Array: Because of the TSI's in the first and the last stage, point-to-point selection is the only possible selection mode (see Section IV-D). Fig. 7 shows the TST array. Expansion is performed by increasing the number of internal time slots  $M^*$ . If  $M^*$  is chosen to  $M^* = 2M - 1$  the array becomes strictly nonblocking [5].

The mapping of a  $T \cdots T$  array will be discussed in the following chapter. Instead of the whole mapped array, the short notation of the equivalent SDM array is shown in Fig. 7.

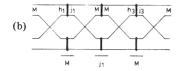

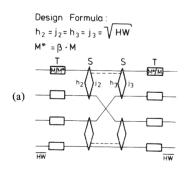

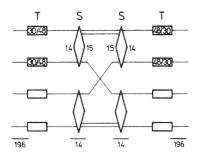

#### D. The Four Stage Switching Array: TSST

The four-stage TSST array, see Fig. 8(a), is the first to allow forming of blocks. Fig. 8(b) shows the mapped array. The same mapping rules hold, as above. One TSI of the first and last stage, respectively, becomes one multiple with M

Fig. 6. (a) STS array. (b) Mapped STS array.

Design Formula

$h_2 = j_2 = HW$  $M^* = \beta \cdot M$

Short Notation

Fig. 7. (a) TST array. (b) Mapped TST array and its short notation.

Fig. 8. (a) TSST array. (b) Mapped TSST array.

inlets and  $M^*$  outlets or vice versa. Normally  $M^*$  is greater than M because of the necessary expansion.

A space switch again becomes a column of M\* multiples with  $h_2$  inlets and  $j_2$  outlets each, if, e.g., the second stage is regarded.

The blocks which are formed between stages 1 and 2 as well as 3 and 4 of the PCM array appear also as blocks within the mapped array. The incoming and outgoing ML's terminate at one TSI: From this it follows that the equivalent trunk group in the mapped array terminates also on only one multiple. Therefore, only point-to-point selection is possible, as one outgoing ML can only be reached via one multiple of the last stage.

The dashed lines between stages 2 and 3 have to be provided if combined switching (cf. Section III-B.) is applied. This is necessary for this switching mode only, as thus the number of possible connections remains constant between all blocks on the left- and the right-hand side, including likewise numbered blocks (one connection requires two paths).

The design formula follows in this case from the prerequisite that all intermediate stages switch 1:1 and the number of incoming and outgoing ML's is the same, namely HW.

This four-stage array can easily be extended from a smaller initial size to the planned final size, if the principle of constant block size is applied [9], [12]. In this case the SS have apriori the final size. For intermediate sizes of the four-stage array with less blocks more than one ML leads from a block on the left-hand side to a block on the right-hand side.

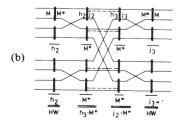

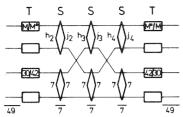

#### E. Five Stage Switching Arrays

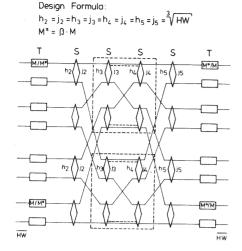

There are four five-stage arrays that fulfill the requirement of being symmetrical: the TSSST, the SSTSS, the STSTS, and the TSTST array.

The last one, however, does not increase the traffic capacity compared with the four-stage array.

1) The TSSST Array: Fig. 9(a) shows the PCM array and Fig. 9(b) the mapped equivalent SDM array. The same design rules as discussed above are applied. Blocks are formed between stages one and two as well as between stages four and five. The appearance of the blocks in the equivalent SDM array is the same as in Section IV-D. The presentation of the middle stage is such that, multiples representing the same timeslot number are adjacent.

The structure of the presented mapped SDM array holds for all five-stage arrays. There are only differences in the number of inlets and outlets of the multiples as well as in the mapping of the incoming and outgoing ML's.

The other two five-stage arrays (Fig. 10(a),11) have S-stages in the first and the last stage. Therefore, in the mapped SDM array, the incoming and outgoing ML's of stage one and five, respectively, terminate at a column of M multiples (cf. Fig. 10(b), 11).

The TSSST array can be extended in the same way as the four-stage array if the space switches are designed for the final

Fig. 9. (a) TSSST array. (b) Mapped TSSST array.

Fig. 10. (a) SSTSS array. (b) Mapped SSTSS array.

Fig. 11. STSTS array.

Design Formula:

2) The SSTSS Array: This array allows forming of blocks between stages two, three, and four [cf. Fig. 10(a)]. Expansion in the first stage is performed by increasing the number of ML's:  $j_1 = \beta \cdot h_1$ . If, in contradiction to the prerequisites, the second stage is also expanded, the array can become strictly nonblocking (the values are:  $j_1 = 2h_1 - 1$ ,  $j_2 = 2h_2 - 1$ ) [5].

The array allows very good extension strategies if the blocks in the middle stages and the space switches are designed for the final size. It is even possible, again in contradiction to the prerequisites, to make only the internal block strictly nonblocking. Then this block could have a control unit of its own and path searching could be simplified because the whole array could be regarded like a three-stage array [19]. Fig. 10(a) shows the PCM array and Fig. 10(b) the equivalent SDM array.

3) The STSTS Array: Fig. 11 shows the STSTS array and the short notation of the mapped array. Again blocks are formed between stages one and two as well as four and five. The extension strategy of this array is the same as above. Quasi-symmetrical path allocation is applied between the two T stages, if combined switching is provided.

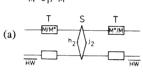

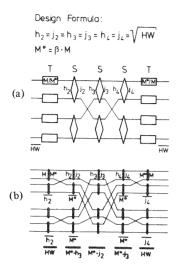

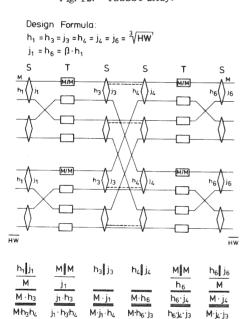

#### F. Six Stage PCM Switching Arrays

- 1) The TSSSST Array: There are different possibilities for the structure of this type of array. The presented array has the minimum amount of costs and can easily be extended, if the blocks and space switches are designed for the final size. As the first and the last stage is a T stage only point-to-point selection is possible. Fig. 12 shows the PCM array, the short notation of the mapped array, and the design formula.

- 2) The STSSTS Array: Blocks can be formed within the first three and the last three stages (cf. Fig. 13). Interconnection between the blocks is performed between stages three and four.

The dashed ML's are necessary for combined switching in order to have the same number of possible connections from each block on the left-hand side to each block on the right-hand side. Between the two T stages quasi-symmetrical path allocation is applied. The extension strategies for this array are the same as discussed above.

Interleaved wiring [9], [16] which can be used in SDM switching arrays to improve the grade of service is not possible because the considered PCM systems must be symmetrically structured. Therefore, the PPL method, which allows the calculation of the point-to-point loss, was slightly modified for five and six stage arrays. [16].

Simulations show that the PPL method offers good results for separated switching as well as for combined switching.

# V. IMPORTANT FEATURES OF PCM SWITCHING ARRAYS

When the choice of a structure and the number of highways to be connected to has been made, the number of ML's terminating in one matrix or block is the only variable remaining free. This variable, however, is responsible for the number

Short Notation M M"  $h_2 j_2$  $h_3$   $j_3$ h<sub>4</sub> j<sub>4</sub> M h<sub>3</sub>·h<sub>2</sub>

TSSSST array. Fig. 12.

Fig. 13. STSSTS array.

$M \cdot j_1 \cdot h_4$

$M \cdot h_6 \cdot j_3$

$h_{6}j_{4}$   $j_{3}$

of blocks and has a great influence on the costs of the whole array.

A related paper [14] presents how this variable has to be chosen to obtain minimum costs for the whole array. The design formulas that have been given for each array result from this optimal choice.

For the following comparisons concerning the quality of the PCM switching arrays, only point-to-point selection will be considered.

#### A. Calculation of the Costs of a PCM Switching Array

The costs for a PCM array are the sum of the costs for all logical gates in the crosspoints of the space switches, the costs for the control memories of the SS, and the costs for

the TSI, i.e., costs for the speech memories and the respective control memories. The costs for the control memories depend on whether a path allocation principle is applied or not. The formulas for the calculation of the costs are given in the annex. For all formulas it is assumed that quasi-symmetrical path allocation for  $T \cdots T$  arrays as well as for  $S \cdots S$  arrays is applied.

To obtain a uniform manner of presentation, a cost ratio (CR) is introduced which is the ratio between the costs for a gate and the costs for a storage bit.

The additional hardware elements, necessary to control the function of the memories and gates can be taken into account by choosing an appropriate value for CR.

For the costs it holds

$-COSTS = CR \cdot G + CMG + SM + CMSM$  (abbreviations explained in the Annex).

To summarize the formulas—The parameters that influence the costs of the PCM switching array are:

- the type of the array,

- the number of highways to be connected to,

- the number of TS per highway,

- combined or separated switching,

- serial or parallel switching,

- the cost ratio CR.

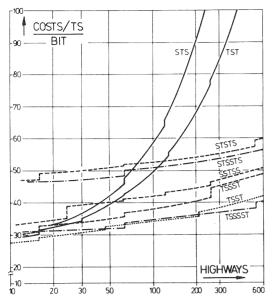

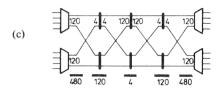

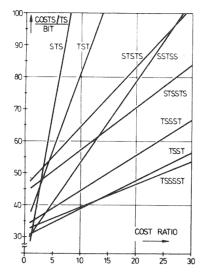

Fig. 14 shows a comparison among the costs of the presented arrays. The number of TS per ML is 30, a cost ratio of 5 is assumed, and combined switching is performed in serial.

All arrays are expanded such that, for a prescribed carried traffic per TS, Y/TS = 0.8 Erlangs. The point-to-point loss is  $B_{pp} \approx 0.1$  percent.

The curves show that both three-stage arrays become rather expensive for increasing highway numbers. This comes from the large space switches heaving  $HW^2$  gates. The discontinuities in these curves, as well as in the other ones, follow from the control bits for addressing the space switches. Whenever the dual coded address requires an additional bit, such a discontinuity appears.

Among the other multistage arrays these arrays are the cheapest which have a T stage as the first and the last one; those with an S stage are more expensive.

There are two reasons for the  $T \cdots T$  arrays to be less expensive.

- The TSI's in the first and last stage are in their mapped form SDM multiples, having a size of about 30/40. Large multiples like these in the first stage favor the grade of serv-

- Expansion is performed by increasing the number of internal TS which is the cheapest expansion mode.

These reasons do not hold for the  $S \cdots S$  arrays.

The economic multiple size in the first stage is relatively small. Therefore, a remarkable expansion is often necessary in order to obtain the prescribed probability of loss; this increases the costs.

To summarize the results of Fig. 14: The above prerequisites hold that  $T \cdots T$  arrays are the most economic ones, having costs of 30 ··· 50 bits/TS (per termination, respectively).

Fig. 14. Relative costs per time slot for different highway numbers Y/TS = 0.8 Erlangs,  $B_{pp} = 0.1$  percent, CR = 5, M = 30 TS/ML, combined, serial switching.

## B. Influence of the Number of TS per ML on the Loss Probability and the Costs

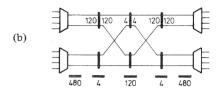

The relative costs for a PCM switching array can be reduced if, having a constant total number of terminations, the number of TS within one ML is increased and, consequently, the number of ML's decreased. The savings in costs lie in the logical gates, as their costs generally remain constant whether they have to switch 30 or 120 TS. The principle of realization is to multiplex several ML's with 30 TS each, into one ML with 120 TS. Fig. 15 shows, as an example, this "multiplexing before switching" for the two types of three-stage arrays.

Fig. 15 (b) and (c) shows the mapped SDM arrays of the TST and STS PCM array. The increased number of TS has quite different effects on the two array types.

For the mapped TST array it holds that the multiples in the first and the last stage become greater, from 30/30 to 120/120. This decreases the loss probability. Fig. 16 shows this effect.

Curve 1 holds for the array with M = 30 TS per ML, Curve 3 for M = 120 TS per ML. Additionally, Curve 2 shows the traffic behavior for M = 60 TS/ML.

If the relative costs are calculated, the following values hold (CR = 5) for the TST array:

- for M = 30 TS/ML the relative costs are 28 bits/TS,

- for M = 120 TS/ML the relative costs are 25 bits/TS.

It should be noticed that the probability of loss as well as the costs/TS decrease if the number of TS/ML is increased from 30 to 120 TS/ML.

The effect is different for the STS array. For 120 TS/ML the multiples in the first stage become smaller, Fig. 15(c) and the loss probability increases (compare curves 4 and 6). However, the costs still decrease (CR = 5):

- for M = 30 TS/ML the relative costs are 22 bits/TS,

- for M = 120 TS/ML the relative costs are 17 bits/TS.

Fig. 15. (a) Multiplexing before switching. (b) Mapped TST array. (c) Mapped STS array.

Fig. 16. Probability of loss for various TST and STS arrays.

The loss probability for M = 60 is additionally depicted.

Therefore, a comparison is necessary between STS arrays, having M=30 and 120 TS/ML, which are expanded such that they have approximately the same probability of loss for the same prescribed traffic per line (here  $Y/n\approx 0.8$  Erlangs and  $B_{pp}\approx 2$  percent).

Fig. 16 shows the resulting curves 7 and 8 and the short notation of these expanded arrays. Their calculated costs are now:

- for M = 30 TS/ML, 28 bits/TS,

- for M = 120 TS/ML, 26 bits/TS.

Fig. 17. Comparison of the relative costs per time slot for different switching modes and various numbers of time slots per highway, n = 4320, Y/TS = 0.8 Erlangs, B<sub>pp</sub> = 0.1 percent, CR = 5, serial switching. CSw: Combined switching ○. SSw: separated switching □.

These costs show that "multiplexing before switching" may also be favorable for STS arrays because of decreasing relative costs. Additionally, a smaller increase of loss in case of overload is obtained for M = 120 TS/ML (cf. curves 7 and 8; Fig. 16).

Further information about the relative costs of STS and TST arrays, respectively, can be found in Fig. 17 and in the PCM charts [15].

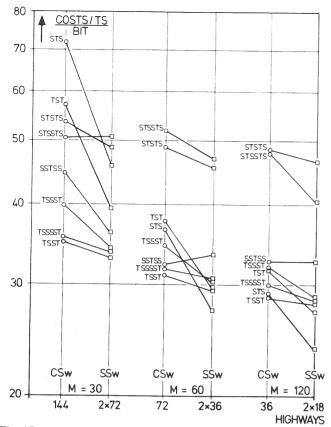

In the following, a comparison concerning the costs is presented between arrays which have a prescribed probability of loss and a constant number of terminations for a prescribed carried traffic per termination.

The constant number of terminations is n = 4320; the traffic per termination is prescribed to 0.8 Erlangs and the point-to-point loss to 0.1 percent. The presented arrays use combined switching as well as separated switching.

It should be noted that the number of terminations is always equal to the number of TS for both switching modes. The calculated relative costs are depicted in Fig. 17 versus different numbers of highways having  $M=30,\,60,\,\mathrm{and}\,120$  TS/ML. The linked values hold for the same total number of highways connected to the array.

First Result: The relative costs of all PCM arrays are reduced if the number M of TS/ML is increased, while the total number of connected terminations remains constant. This holds for combined switching, denoted in the figure by circles as well as for separated switching, denoted in the figure by squares. The decrease of the costs is essentially due to the fact

that the space switches become smaller whereas the costs per gate remain constant, independent of whether 30 or 120 TS have to be switched. The number of control memory bits for the gates is reduced and for the speech memories it is increased. Due to this increase, it may sometimes be possible that the savings of the space switches are compensated for by additional costs for the TSI's. This is particularly so if the SS and the CR are small.

Second Result: The figure shows that separated switching is generally cheaper than combined switching represented by the falling lines between the circles and the squares. However, separated switching does not allow connections to be established between all highways. The decrease of the costs is again due to the fact that the SS become smaller as only half of the highways are connected to one array (constant number of terminations provided).

There are some exceptions, however, e.g., the SSTSS array with M=60. There are savings in the number of gates but additional costs are necessary for control memories that compensate the savings.

Third Result: The cost relation among the discussed arrays changes with the number of TS per ML.

For combined switching with 144 highways, the values are the same as in Fig. 14 for HW = 144.

For M = 30, the three-stage arrays are rather expensive and the four-stage array is the cheapest.

For M=60, the STSTS and STSSTS array become most expensive. Again the reasons are the small SS and the great expansion necessary to obtain the prescribed loss probability. These two arrays remain expensive also for the other values of M, as this effect cannot be reduced.

For M=120, the costs of all arrays are smaller. The consequence is such that if "multiplexing before switching" is not too expensive it should be applied.

#### C. Influence of the Cost Ratio

The influence of the cost ratio is the last to be discussed. Up to now all comparisons have been based on CR = 5 = constraint. The influence of the various CR on the arrays having 144 highways is shown in Fig. 18. Of course, the costs of all arrays increase with an increasing cost ratio. The strongest increase suffers the three-stage arrays; the smallest increase holds for the  $T \cdots T$  arrays. The decision, which cost ratio has to be assumed in practice, depends on the momentary technological standard as well as on the additional hardware costs for the control of the elements.

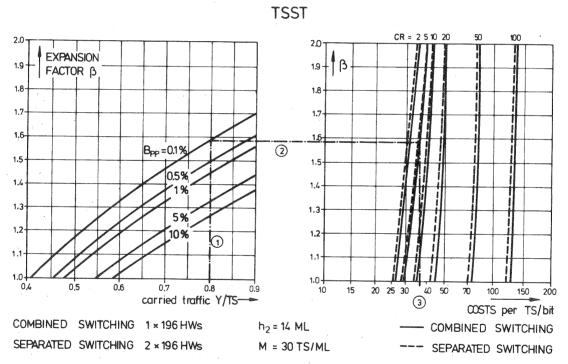

#### VI. DESIGN OF ECONOMIC PCM SWITCHING ARRAYS BY MEANS OF THE PCM-CHARTS

In order to support field engineers in choosing the best suited PCM switching arrays for a certain application, a booklet with a large number of PCM charts was edited [15]. These PCM charts allow the design of economic switching arrays for various numbers of highways and different values of M time slots (TS) per multiplex line. When the desired probability of loss for the prescribed carried traffic per time slot Y/TS (equal to the carried traffic per termination) is chosen, the array can be constructed.

Fig. 18. Influence of the cost ratio CR, HW = 144, M = 30 TS/ML, Y/TS = 0.8 Erlangs,  $B_{pp} = 0.1$  percent, combined, serial switching.

Fig. 19. PCM chart for a TSST array.

Its resulting relative costs for different cost ratios can also be found in the charts. Fig. 19 shows a PCM chart of one four-stage array.

The left chart shows the expansion of the array versus the carried traffic per TS, the probability of loss is the curve parameter. The curves hold for a PCM array using combined switching having 196 highways and for an array using separated switching having 2 • 196 highways. The right chart shows the necessary costs for a given expansion; parameter for the curves is the cost ratio CR. The bold line holds for combined switching, the dashed line for separated switching. It should be noted that the array for separated switching has double the number of terminations.

The use of the charts will be shown by means of the following example.

A four stage PCM array is to be designed. The final size should allow 196 highways to connect with M=30 TS each; combined switching is performed and CR is 5.

The required probability of loss for a prescribed Y/TS of 0.8 Erlangs is  $B_{pp} = 0.1$  percent.

Step 1) The necessary expansion can be found in the left chart; its value is about 1.6. This value, together with  $h_2 = 14$  allows the design of the PCM array, see Fig. 20. The additional "horizontal" ML's are necessary as combined switching is required. The expansion is performed by increasing the number of internal TS from 30 to 48.

Fig. 20. Design example for the TSST array, Y/TS=0.8 Erlangs,  $B_{pp}=0.1$  percent, combined, serial switching.

Step 2) The resulting costs for different cost ratios can be found in the right chart.

Step 3) For CR = 5, the costs are about 35 bits/TS.

#### VII. SUMMARY

Symmetrical PCM switching arrays having one to six stages have been discussed in the paper. It was shown how the PCM arrays can be mapped into equivalent SDM arrays to simplify the calculation of their probability of loss. The relative costs of the PCM arrays have been calculated applying different switching modes. Design formulas are given which are derived in the related paper [14]. The paper concludes in presenting new PCM charts for the quick and economic design of PCM switching arrays.

#### VIII. ANNEX

Formulas are given to calculate the amount of gates (G), the amount for their control memories (CMG), the number of speech memories (SM) and their control memories (CMSM). The equations have a general form in order to allow their application also if, e.g., additional ML's have to be provided. The prerequisite of symmetrically structured arrays is already implemented.

Abbreviations and Prerequisites:

G: number of gates

CMG: number of control memory bits for the gates

SM: number of speech memory bits

CMSM: number of control memory bits for the SM's

M: number of time slots per multiplex line E: separated switching E = 2

E = 2 combined switching E = 2

P: switching in serial P=1 parallel switching P=8

β : expansion is always performed in the first and concentration in the last stages, intermediate

stages switch 1:1

lda: logarithmus dualis  $log_2 a$

Q: allocation principle within  $S \cdots S$  arrays

symmetrical allocation Q = 1 quasi-symmetrical allocation Q = 0.5

• the number of incoming and outgoing ML is identical,

• switching arrays are structured symmetrically,

• the forming of blocks is as discussed above.

TST:

$G = h_2^2 \cdot E \cdot P$   $CMG = h_2 \cdot \beta \cdot M \cdot ld \ h_2^1$   $SM = h_2 \cdot M \cdot 2 \cdot 8 \cdot E$   $CMSM = h_2 \cdot \beta \cdot M \cdot E \cdot ld \ M$

STS:

$G = h_1 \cdot j_1 \cdot 2 \cdot E \cdot P$   $CMG = h_1 \cdot M \cdot E \cdot ld j_1$   $SM = j_1 \cdot M \cdot 8 \cdot E$   $CMSM = j_1 \cdot M \cdot Q \cdot ld M$

TSST:

$\begin{array}{lll} G & = & HW \cdot j_2 \cdot 2 \cdot E \cdot P \\ CMG & = & HW \cdot \beta \cdot M \cdot E \cdot ld \ j_2 \\ SM & = & HW \cdot M \cdot 2 \cdot 8 \cdot E \\ CMSM & = & HW \cdot \beta \cdot M \cdot E \cdot ld \ M \end{array}$

TSSST:

$G = (HW \cdot j_2 \cdot 2 + h_3 \cdot j_3 \cdot j_2) \cdot E \cdot P$

$CMG = HW \cdot \beta \cdot M \cdot E \cdot ld j_2 + j_2 \cdot h_3 \cdot \beta \cdot M \cdot ld h_3$

$SM = HW \cdot M \cdot 2 \cdot 8 \cdot E$  $CMSM = HW \cdot \beta \cdot M \cdot E \cdot 1dM$

SSTSS:

$G = (HW \cdot j_1 \cdot 2 + h_2 \cdot j_2 \cdot j_1 \cdot 2) \cdot E \cdot P$   $CMG = (ld j_1 + \beta \cdot ld j_2) \cdot HW \cdot M \cdot E$

$SM = j_1 \cdot j_2 \cdot M \cdot 8 \cdot E$   $CMSM = j_1 \cdot j_2 \cdot M \cdot Q \cdot ld M$

STSTS:

$G = (HW \cdot j_1 \cdot 2 + h_3 \cdot j_3 \cdot j_1) \cdot E \cdot P$   $CMG = (E \cdot ld \ j_1 + \beta \cdot ld \ j_3) \cdot HW \cdot M$

$SM = HW \cdot \beta \cdot M \cdot 2 \cdot 8 \cdot E$  $CMSM = HW \cdot \beta \cdot M \cdot E \cdot IdM$

TSSSST:

$G = (HW \cdot j_2 \cdot 2 + 2 \cdot h_3^2 \cdot j_3 \cdot j_2) \cdot E \cdot P$

$CMG = (HW \cdot \beta \cdot M \cdot ld j_2 + j_2 \cdot h_3^2 \cdot \beta \cdot M \cdot ld j_3) \cdot E$

$SM = HW \cdot M \cdot 2 \cdot 8 \cdot E$  $CMSM = HW \beta \cdot M \cdot E \cdot ld M$

STSSTS:

$G = (HW \cdot j_1 \cdot 2 + h_3^2 \cdot j_3 \cdot j_1) \cdot E \cdot P$   $CMG = (HW \cdot M \cdot ld \ j_1 + HW \cdot \beta \cdot M \cdot ld \ j_3) \cdot E$

$SM = HW \cdot \beta \cdot M \cdot 2 \cdot 8 \cdot E$  $CMSM = HW \cdot \beta \cdot M \cdot E \cdot IdM$

Example: In order to show the use of these formulas, a TSSST array will serve as an example for the calculation of

<sup>1</sup> Whenever ld a is used, it has to be checked whether or not the result is an integer value. If not, the next greater integer value has to be chosen for the calculation of the number of bits.

Fig. 21. TSSST array with 49 highways as an example for the calculation of the relative costs.

the different values. In Fig. 21 the considered array is depicted; combined and serial switching is applied (E = 1,P=1). The expansion is chosen such that  $B_{pp}=0.1$  percent for Y/TS = 0.8 Erlangs is achieved.

$$G = (HW \cdot j_2 \cdot 2 + h_3 \cdot j_3 \cdot j_2) \cdot E \cdot P$$

=  $(49 \cdot 7 \cdot 2 + 7 \cdot 7 \cdot 7) \cdot 1 \cdot 1$

=  $1029$

$$CMG = HW \cdot \beta \cdot M \cdot E \cdot ld_{j2} + j_2 \cdot h_3 \cdot \beta \cdot M \cdot ld h_3$$

$$= 49 \cdot 42 \cdot 1 \cdot 3 + 7 \cdot 7 \cdot 42 \cdot 3$$

$$= 12348$$

$$SM = HW \cdot M \cdot 2 \cdot 8 \cdot E$$

$$= 49 \cdot 30 \cdot 2 \cdot 8 \cdot 1$$

$$= 23520$$

$$CMSM = HW \cdot \beta \cdot M \cdot E \cdot ld M$$

$$= 49 \cdot 42 \cdot 1 \cdot 5$$

$$= 10290$$

Assuming a cost ratio CR = 5, the resulting relative costs are (compare also Fig. 14)

COSTS per TS =

$$(1029 \cdot 5 + 12348 + 23520 + 10290)(49 \cdot 30)$$

=  $34.92 \text{ bits/TS}$ .

#### **ACKNOWLEDGMENT**

The authors would like to express their thanks to Prof. Dr. A. Lotze and Dr. A. Röder and Dr. G. Thierer, as well as to Dr. J. Sagebarth for his help in writing the computer program system.

#### REFERENCES

- [1] D. Bazlen, G. Kampe, and A. Lotze, "On the influence of hunting mode and link wiring on the loss of link systems," in Proc. 7th Int. Teletraffic Cong., Stockholm, Sweden, 1973, pp. 232/1-12; also in "Information transmission" (in Russian), Inform. Express, no. 35, pp. 11-39, Sept. 1973, Moscow, Russia.

- "Design parameters and loss calculation of link systems," IEEE Trans. Commun., vol. COM-22, pp. 1908-1920, Dec. 1974.

- [3] E. S. Bieszczad, R. F. Kowalik, K. E. Krylow, and M. Macrander, "No. 3EAX network and master clock," GTE Automat. Elec. J., July 1977.

- [4] J. P. Coudreuse, P. Grall, and C. Raphalen, "Système E10 centres de transit temporels," Commutation et Electronique, no. 43, Oct.

- [5] C. Clos, "A study of nonblocking switching networks," Bell Syst. Tech. J., vol. 32, pp. 406-424, 1953.

- R. K. Holm, "No. 3EAX description," GTE Automat. Elec. J., July 1977.

- M. Huber, "On the congestion in TDM systems," in Proc. 4th Int. Teletraffic Cong., London, England, 1964, Doc. 104.

- A. W. Kobylar, "Methodology for isolating a set of near optimum PCM digital network configurations," in Proc. Int. Commun. Conf., Minneapolis, MN, 1974, pp. 34E1-5.

- A. Lotze, A. Röder, and G. Thierer, "PPL—A reliable method for the calculation of point-to-point loss," in *Proc. 8th Int. Teletraffic* Cong., Melbourne, Australia, 1976, pp. 547/1-14; also in Proc. Int. Commun. Conf., Chicago, IL, 1977, vol. 1, pp. 213-226.

- -, "Investigations on folded and reversed link systems," in Proc. 8th Int. Teletraffic Cong., Melbourne, Australia, 1976, pp. 544/1-5; also in Proc. Int. Commun. Conf., Chicago, IL, 1977,

- vol. 1, pp. 232–236.

—, "Point-to-point selection versus point-to-group selection in [11] link systems," in Proc. 8th Int. Teletraffic Cong., Melbourne, Australia, 1976, pp. 541/1-5; also in Proc. Int. Commun. Conf., Chicago, IL, 1977, vol. 1, pp. 227-231.

- "Nik-charts for the design of link systems operating in the point-to-point selection mode or point-to-group selection mode,' Inst. Switching and Data Technics, Univ. Stuttgart, Germany, ISBN 3-922403-06-9, 1976.

- -, "Point-to-point loss in case of multiple marking attempts," [13] Inst. Switching and Data Technics, Univ. Stuttgart, Germany,

- [14] A. Lotze, K. Rothmaier, R. Scheller, "TDM versus SDM switching arrays-A comparison," in Proc. 9th Int. Teletraffic Cong., Torremolinos, Spain, 1979, IEEE Trans. Commun., to be

- ..., "PCM charts for the design of economic PCM switching arrays," Inst. Switching and Data Technics, Univ. Stuttgart, Germany, ISBN 3-922403-07-7, 1979.

- [16] G. Thierer, "The calculation of the probability of loss in link systems with point-to-point selection," report on studies in congestion theory, Inst. Switching and Data Technics, Univ. Stuttgart, Germany, Rep. 29, ISBN 3-922403-39-5, 1980.

- [17] J. Postollec, "Le réseau de connexion de Système E10," Commutation et Electronique, no. 40, Jan. 1973.

- [18] T. Saito, "An optimum design theory for PCM toll switching networks," in Proc. Nat. Telecommun. Conf., 1977, Los Angeles, CA, pp. 46:1-6.

- [19] R. Scheller and M. Wizgall, "A local PCM switching system for voice and data," in *Proc. ISS'76*, Paris, France, pp. 419–426.

- [20] M. Tanaka, "Nonblocking switching in integrated PCM networks," in Proc. 6th Int. Teletraffic Cong., München, Germany, 1970, pp. 477-478.

- [21] H. E. Vaughn, "An introduction to no. 4 ESS," in Proc. ISS, Cambridge, England, 1972, pp. 19-25.

- [22] P. Voyer, M. Ballard, and B. Ledieu, "Réseaux de connexion temporels a grande capacité," Commutation et Electronique, no. 43, Oct. 1973.

Klaus Rothmaier received the M.S. degree in electrical engineering from Stuttgart University, Stuttgart, West Germany, in 1978.

Since then he has been Assistant Professor at the Institute of Switching and Data Technics, University of Stuttgart. His current activities are in the field of PCM-Switching techniques with emphasis on teletraffic theory and path searching algorithms.

Reinhard Scheller received the M.S. and the Ph.D. degrees in electrical engineering from Stuttgart University, Stuttgart, West Germany, in 1975 and 1981, respectively.

Since 1975 he has been Assistant Professor at the Institute of Switching and Data Technics, Stuttgart University, where he worked primarily in the field of PCM-Switching techniques. This work includes the teletraffic-theoretical aspect of the switching networks as well as investigations on control mechanisms and realization.