# CAD-gestützter Schaltungs- und Layoutentwurf in Forschung und Lehre

W.W. Lemppenau

M.J. Schröder

Institut für Nachrichtenvermittlung und Datenverarbeitung Universität Stuttgart 7000 Stuttgart 1, Seidenstraße 36

#### Übersicht

CAD¹-Systeme sind aus vielen Bereichen der Ingenieurwissenschaften nicht mehr wegzudenken. Um Studenten in den CAD/CAE² gestützten Entwurf von elektronischen Schaltungen einzuführen wurde am Institut für Nachrichtenvermittlung und Datenverarbeitung (IND) eine hierarchische CAD/CAE Infrastruktur bereitgestellt. Diese Infrastruktur ist typischerweise auf die Ausbildung von Studenten ohne Vorkenntnisse ausgerichtet.

Der Beitrag beschreibt die historische Entstehung, die hierarchische Struktur und Arbeitsweise innerhalb der Entwicklungsumgebung. Der Einsatz des CAE-Toolpakets LOG/iC<sup>3</sup> zur Entwicklung programmierbarer Logikbausteine innerhalb dieser Hardware-Umgebung und die Einbettung in den logischen Entwurfsablauf einer Hardware-Baugruppe wird vorgestellt. Der Beitrag schließt mit Fallbeispielen aus Studienbzw. Diplomarbeiten und einem Ausblick auf die am Institut durchgeführten, rechnerunterstützten VLSI-Entwicklungsaktivitäten.

## 1. Einleitung

In der Lehre obliegt dem Institut die Aufgabe, die Studenten der Elektrotechnik in die grundlegenden Konzepte der Informationstechnik einzuführen [19]. Dies umfaßt im einzelnen die Lehrveranstaltungen:

- Einführung in die Informatik I und II

- Datenverarbeitung I und II

- Codierung zur Fehlererkennung und Fehlerkorrektur

- Automatentheorie

- Programmiersprachen und Compiler

- $\bullet\,$  System programme I und II

Innerhalb dieser Lehrveranstaltungen werden die grundlegenden Strukturen sowie Hardund Software-Konzepte für den Aufbau von Computersystemen eingeführt. Ergänzend zu den Lehrveranstaltungen werden Versuche im Rahmen des Grundlagen- und des Fachpraktikums Datenverarbeitung angeboten. Das Institut führt jährlich ca. 60 Semesterund Diplomarbeiten durch, davon ca. 30% auf dem Gebiet der Hard- und Firmware-Entwicklung.

<sup>::</sup> engl. Computer Aided Design.

<sup>2:</sup> engl. Computer Aided Engineering.

<sup>3:</sup> Produktname der Firma Isdata, Karisruhe [11].

Das zweite Lehrgebiet des Instituts betrifft die Kommunikationsnetze. Hierfür bietet das Institut folgende Lehrveranstaltungen an :

- · Nachrichtenvermittlung I und II

- Vermittlungstechnik in digitalen Netzen

- Merkmale und Betrieb von Nachrichtennetzen

- Koppelnetze der Vermittlungstechnik

- Wartezeitprobleme

Diese Lehrveranstaltungen sind grundlegender Unterbau für die Forschungsgebiete des Instituts, welche u.a. die schnellen lokalen Rechnernetze, das öffentliche diensteintegrierende Digitalnetz ISDN<sup>4</sup> sowie zukünftige breitbandige Kommunikationsnetze zum Gegenstand haben, einschließlich der hierzu erforderlichen Disziplinen der Protokollarchitektur, des Software-Engineering, der Leistungsanalyse und der modellhaften Implementierung neuer Konzepte in Hard- und Software.

In der Forschung befaßt sich das Institut mit der Theorie, den Entwurfsverfahren, der Modellierung, den Leistungsuntersuchungen sowie der Implementierung neuer Kommunikationsnetze und deren Architekturen [8]. Anwendungen hierfür sind lokale Breitbandnetze für Rechner- und Bürokommunikation, die integrierte Fertigung<sup>5</sup> sowie Verkehrssysteme.

Die einzelnen Forschungsaktivitäten werden von allen Großfirmen der informationstechnischen Industrie, der DFG<sup>6</sup>, dem BMFT<sup>7</sup> sowie der Europäischen Kommission im Rahmen von RACE<sup>8</sup>, ESPRIT<sup>9</sup>, PROMETHEUS<sup>10</sup> und anderen EUREKA Forschungsprojekten unterstützt [8]. Laufende Forschungsvorhaben berühren insbesondere die problemspezifische Entwicklung von Hardware-Komponenten in breitbandigen Kommunikationsnetzen.

In nahezu allen Bereichen der Computer-, Kommunikations-, Automatisierungs- aber auch der Energietechnik werden heute mikroelektronische Komponenten für Steuerzwecke eingesetzt. Der Entwicklungsingenieur muß in der Lage sein, einerseits ein Systemkonzept für die gegebene Steuerungsaufgabe zu entwerfen und andererseits das entworfene Konzept in Hard- und Software zu realisieren. Zur effizienten Lösung der Probleme sind hierbei in der Regel problemangepaßte Schaltungskonzepte zu entwickeln, die einerseits auf hochintegrierten Standardelementen wie Mikroprozessoren, Speichern, programmierbaren Logikbausteinen<sup>11</sup> und Halbleitern für die Leistungselektronik basieren, andererseits aber auch anwendungsspezifische integrierte Schaltungen miteinbeziehen.

<sup>4:</sup> engl. Integrated Services Digital Network.

<sup>5:</sup> auch CIM genannt (engl. Computer Integrated Manufacturing).

<sup>&</sup>lt;sup>5</sup>: Deutschen Forschungsgemeinschaft.

<sup>7:</sup> Bundesministerium für Forschung und Technologie.

<sup>3:</sup> engl. Research and Development in Advanced Communications Technologies in Europe.

<sup>3:</sup> engl. European Strategic Programme for Research and Development in Information Technology.

<sup>10:</sup> Program for an European Traffic with Highest Efficiency and Unprecendented Safety.

<sup>11:</sup> im nachfolgenden EPLD genannt, (engl. Erasable Programmable Logic Device), siehe Abschnitt 3.

Kernpunkte der wissenschaftlichen Hochschulausbildung auf dem Gebiet der Informationstechnik müssen deshalb sein:

- Beherrschung der grundsätzlichen Schaltungstechniken für digitale Schaltungen

- Kenntnis der Rechnerarchitekturen einschließlich der Rechnerorganisation und Betriebssystemkonzepte

- Beherrschung der theoretischen Grundlagen des Systementwurfs und dessen Umsetzung in Hard- und Software

- Kenntnisse und Erfahrungen im Entwurf von hochintegrierten Digitalbausteinen und dichtgepackten Platinen für integrierte Bausteine<sup>12</sup>

- Test digitaler Bausteine und Systeme.

## 2. Aufbau einer Entwicklungsumgebung

Bei der Implementierung von Laborprototypen wurde bis ca. Mitte der achtziger Jahre die Fädeldrahttechnik oder die Wraptechnik eingesetzt [5,7,24]. Typische Merkmale dieser Techniken sind:

- + eine hohe Packungsdichte ist erreichbar

- ÷ Schaltungen mit hohen Taktraten sind vergleichsweise leicht zu implementieren

- + die Plazierung einzelner Komponeneten ist typischerweise unkritisch

- + nachträgliche Erweiterungen bzw. Änderungen können leicht durchgeführt werden

- die Dokumentation wird im Nachhinein erstellt

- die Dokumentation stimmt typischerweise nicht mit der tatsächlichen Schaltung überein

- eine zuverlässige Reproduktion ist nicht erreichbar.

In der ersten Hälfte der achtziger Jahre wurde begonnen, eine manuelle Layouttechnik am IND einzuführen. Diese Technik ermöglicht auf der einen Seite eine zuverlässige Reproduktion einzelner Baugruppen. Dies ist am IND insoweit von großer Wichtigkeit, da Systemimplementierungen typischerweise auf bestimmten Basisbaugruppen aufbauen, welche entweder mehrfach innerhalb eines Systemes benötigt oder durch kleine Erweiterungen individuell den besonderen Anforderungen angepasst werden [10]. Auf der anderen Seite ist diese Layouttechnik am IND dadurch gekennzeichnet, daß manuell zuerst der Schaltungsentwurf vollständig auf Papier durchgeführt wird. Danach werden manuell im Masstab 3:1 auf DIN A0 großen Folienblättern die einzelnen Bauteile plaziert und die Schaltung in Zwei- oder Mehrlagentechnik entflochten und geklebt [6,15,20,26].

Neben der oben aufgeführten einfachen Reproduktion der Baugruppen ist aber diese Vorgehensweise weiterhin durch folgende Nachteile zekennzeichnet:

<sup>12:</sup> im nachfolgenden auch IC genannt, (engl. Integrated Circuit).

- · die Packungsdichte bei Zweilagentechnik ist gering

- die Plazierung einzelner Komponeneten erfolgt nicht optimal, da oft bei Studenten keine Layouterfahrung vorhanden ist

- nachträgliche Erweiterungen bzw. Änderungen sind nur schwer durchführbar

- · die Dokumentation wird im Nachhinein erstellt

- die Dokumentation stimmt typischerweise nicht mit der tatsächlichen Schaltung überein.

Im Jahre 1984 wurde deshalb damit begonnen, den gesamten Entwurfsprozeß hinsichtlich Schaltungsdesign und Platinenlayout in eine Entwicklungsumgebung einzubetten, welche in allen Entwicklungsstufen und für alle -schritte eine Rechnerunterstützung ermöglicht.

## 3. Hierarchische Entwicklungsumgebung

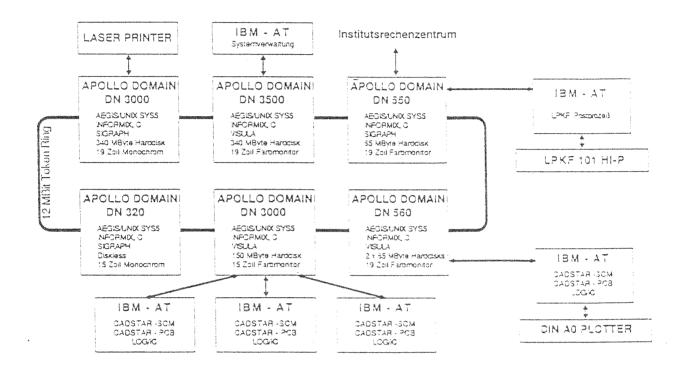

Für zeitintensive Arbeiten wie Schaltplaneingabe, Logikentwurf bzw. Simulation programmierbarer Logikbausteine und Plazierung der Bauteile bei einem Layoutentwurf stehen den Studenten am IND mehrere Arbeitsplatzrechner auf der Basis von IBM-PC zur Verfügung. Diese Rechner zeichnen sich dadurch aus, daß sie weitverbreitet bzw. einfach zu handhaben sind und die darauf verfügbaren CAD-Applikationen bereits eine beachtliche Leistungsfähigkeit besitzen. Bewirkt die Komplexität der zu bearbeitenden Aufgabe für den Fall einer Layoutentwicklung eine ineffiziente Arbeitsweise auf den PCs, so ist eine Weiterführung des Projektes auf einem leistungsstarken Rechnerverbund, bestehend aus mehreren Apollo-Domain Workstations in Cluster-Konfiguration, zu jedem Zeitpunkt und bei jedem Layout-Entwurfschritt möglich. Abbildung 1 zeigt die Struktur dieser Entwicklungsungebung.

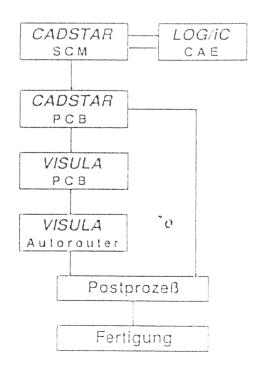

Abbildung 2 zeigt den logischen Ablauf eines Entwurfes auf der Basis der hierbei verwendeten Programmpakete. Mit Hilfe des Programmpakets LOG/iC erfolgt die logische Entwicklung der im Design eingesetzten EPLDs [11].

Die Entwicklung der EPLDs nimmt eine zentrale Stellung im Entwurfsprozeß am IND ein, da ein Einsatz von EPLDs signifikante Vorteile beinhaltet:

- die Anzahl von im Design benötigten ICs kann sehr stark reduziert werden

- Korrekturen von Designfehler können typischerweise durch eine Neuprogrammierung von EPLDs durchgeführt werden; eine manuelle, mechanische Nachbearbeitung von Signalbahnen auf der Leiterplatte entfällt

- Werden nicht alle Ausgänge eines EPLDs von Beginn des Entwurfes verwendet, können zusätzliche Funktionen sehr einfach ohne ein weiteres Hinzufügen von ICs realisiert werden.

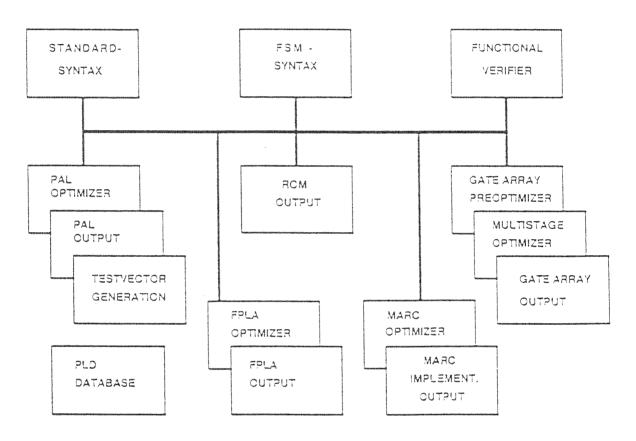

Abbildung 3 zeigt alle den Studenten verfügbaren LOG, iC-Tools. Unabhängig von der späteren, tatsächlichen Realisierung erfolgt in einem ersten Schritt die Beschreibung der

Abbildung 1: Hierarchische Systemstruktur und Entwicklungsumgebung

Abbildung 2: Logischer Ablauf eines Entwurfes

zu entwickelnden Logik durch eine Standard- bzw. FSM-Syntax<sup>13</sup>. In einem zweiten Schritt ist dann durch eine LOG/iC-interne Datenschnittstelle die wahlweise Realisierung durch z.B. PAL-<sup>14</sup>, PLA-<sup>15</sup>, IFL-<sup>16</sup>, PROM-<sup>17</sup> oder Gate-Array-Bausteine bzw. MARC-Strukturen<sup>18</sup> möglich. Die Programmierung der Logikbausteine erfolgt durch ein universelles Programmiersystem, welches an einem der IBM-PCs angeschlossen ist, siehe auch Abbildung 1.

Abbildung 3: Programmpaket LOG/iC

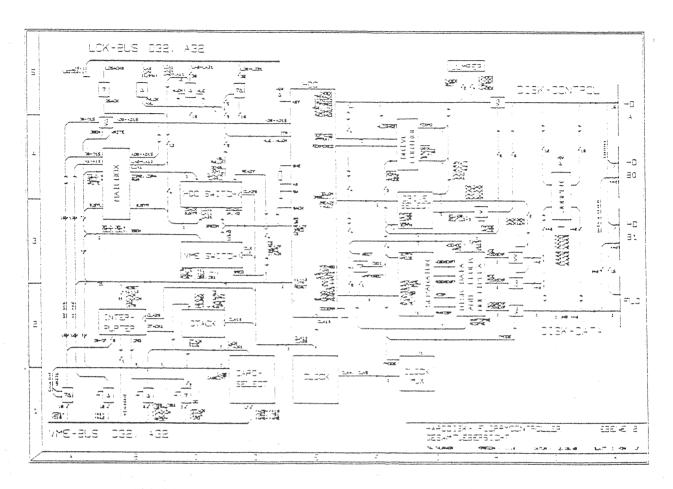

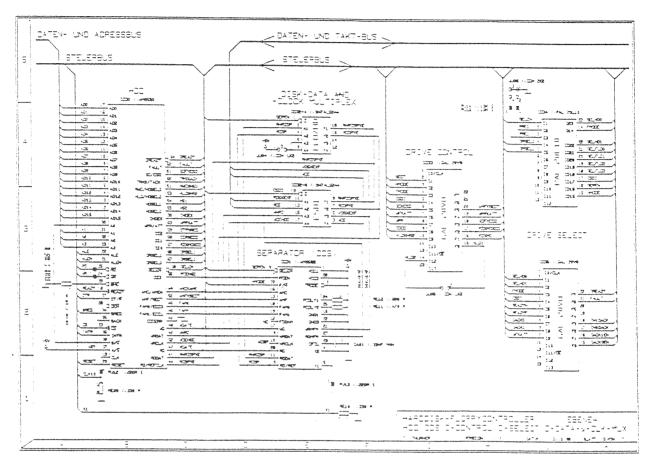

Parallel zum logischen Entwurf der programmierbaren Logikbausteine erfolgt der Schaltungsentwurf mit Hilfe von CADSTAR-SCM<sup>19</sup>. Dieses Programm ermöglicht die graphische Eingabe von Stromlaufplänen und wird auf den PCs eingesetzt. Dieser Schaltungsentwurf erfolgt in einer hierarchischen Top-Down-Vorgehensweise, welche von CADSTAR-SCM in breitem Umfang unterstützt wird. Hierzu zeigen die Abbildungen 4 und 5 repräsentativ einen Ausschnitt aus typischen Diplomarbeiten [17,21].

<sup>13:</sup> Finite State Machine, FSM.

<sup>14:</sup> engl. Programmable Array Logic.

<sup>15:</sup> engl. Programmable Logic Array.

<sup>18:</sup> engl. Integrated Fuse Logic.

<sup>&</sup>lt;sup>17</sup>: engl. <u>P</u>rogrammable <u>R</u>ead <u>O</u>nly <u>M</u>emory.

<sup>18:</sup> engl. Minimized Address Space ROM Based Controller.

<sup>19:</sup> Produktname der Firma Racal-Redac, [3].

Abbildung 4: Hierarchischer Schaltungsentwurf (Ebene 2)

Nach der Fertigstellung der gesamten Schaltung wird der Stromlaufplan in einen Eingabedatensatz für das Entflechtungsprogramm CADSTAR-PCB<sup>20</sup>, umgesetzt. Dieses Programm ermöglicht die Plazierung der Bauteile und die Entflechtung der Signal- und Stromversorgungsbahnen innerhalb einer Leiterplatte und wird ebenfalls auf den PCs eingesetzt. Bewirkt die Komplexität des Layouts eine ineffiziente Arbeitsweise auf den IBM-PCs, so werden der Datensatz des Schaltplanes oder der aktuelle Layout-Datensatz zu einer der Workstations übertragen und dort das Layout mit Hilfe des Programmes VISULA<sup>21</sup>, vervollständigt.

Wesentliche Vorraussetzung für einen konfliktfreien Transfer ist hierbei die Konsistenz der einzelnen Datenbanken der CADSTAR-Programme auf den jeweiligen PCs und der zentralen, relationalen Datenbank der VISULA-Programme. Sowohl der Nutzdatentransfer als auch die Gewährleistung der Datenbankkonsistenz erfolgt mit Hilfe von Programmpaketen, welche im Rahmen von Semesterarbeiten am IND selbst entwickeit und implementiert wurden [9,14].

Die der Entslechtung nachgeordneten Postprozesse ermöglichen die Erzeugung aller benö-

<sup>&</sup>lt;sup>20</sup>: Produktname der Firma Racal-Redac, [4].

<sup>&</sup>lt;sup>21</sup>: Produktname der Firma Racal-Redac, [22].

Abbildung 5: Hierarchischer Schaltungsentwurf (Ebene 4)

tigter Produktionsdaten für eine automatisierte Fertigung der Leiterplatten. Bei Leiterplatten mit Mehrlagentechnologie erfolgt die Fertigung durch externe Leiterplattenhersteller mit Hilfe der auf Datenträger wie Floppy-Disk, Magnetband o.ä. eingereichten Produktionsdaten.

Die Fertigung von Leiterplatten in Zweilagentechnologie erfolgt am Institut in drei Schritten:

- $\bullet$ auf der Basis der erzeugten Produktionsdaten werden direkt mit Hilfe eines Fräsbohrplotters^22 die Bohrlöcher gebohrt  $^O$

- nach dem Bohren der Bohrlöcher werden diese mit Hilfe einer vier Bäder-Galvanisierung<sup>23</sup> durchkontaktiert

- nach dem Durchkontaktieren werden direkt mit Hilfe der erzeugten Produktionsdaten die Leiterbahnen für beide Seiten bzw. die Platinenumrandung herausgefräst und die Bohrlöcher ohne Durchkontaktierung gebohrt.

<sup>22:</sup> LPKF-Frasbohrplotter 101 HI-P, [12].

<sup>23:</sup> LPKF-Contac. [13].

## 4. Bisher gewonnene Erkenntnisse

5 Jahre praktischer Einsatz und ca. 60 Studien- und Diplmomarbeiten führen zu folgenden Erkenntnissen:

Die größten Schwierigkeiten bei der Einführung einer CAD-gestützten Entwicklungsumgebung stellt die Erstellung der benötigten Datenbank dar. Von allen CAD-Programmhersteller werden zwar entsprechende Datenbanken angeboten, jedoch hat es sich herausgestellt, daß auch heute keine der am Markt verfügbaren Datenbanken die jeweiligen individuellen Anforderungen, vor allem hinsichtlich der Produktionstechnologien, erfüllen<sup>24</sup>.

Nach der Erarbeitung mehrerer Benutzerhandbücher [1,16,23,25], welche alle Anforderungen an eine studentische Arbeitsweise berücksichtigen, kann eine vollständige Einarbeitung eines neu mit den Programmpaketen CADSTAR-SCM und -PCB arbeitenden Studenten in weniger als zwei Wochen durchgeführt werden.

Durch die hierarchischen Top-Down-Vorgehensweise werden effiziente Schaltungskonzepte als auch nachvollziehbare Schaltungsentwürfe gefördert

Durch die vollständige Rechnerunterstützung bei allen Entwurfschritten ist eine Konsistenz der Dokumentation mit der tatsächlich realisierten Lösung weitestgehend gewährleistet.

Durch die hierarchische Struktur der Entwicklungsumgebung und der erarbeiteten Durchgängigkeit der Nutzdaten kann jede Schaltungskomplexität mit der hierfür notwendigen Rechnerleistung automatisiert entflochten werden. Damit sind kritische Punkte wie Plazierung als auch zeitintensives manuelles Entflechten von untergeordneter Bedeutung.

Die Durchführung von Studienarbeiten an den Workstations hat sich als nicht sinnvoll herausgestellt. Neben dem Betriebssystem bedeutet schon die Einarbeitung in das hier eingesetzten Programmpaket VISULA für eine große Anzahl von Studenten einen wesentlichen Anteil ihrer für die Semesterarbeit zur Verfügung stehenden Arbeitszeit<sup>25</sup>. Dies zeitliche Einschränkung gilt jedoch nicht für Diplomarbeiten<sup>26</sup>.

Einschließlich aller Rüstzeiten dauert die Fertigung von zweiseitigen Einfacheuropa- bzw. Doppeleuropaplatinen typischerweise zwischen zwei bis drei Stunden. Der Aufbau einer Baugruppe kann damit am selben Tag der Layout-Fertigstellung erfolgen.

#### 5. Ausblick

Anwendungspezifische höchstintegrierte Schaltungen<sup>27</sup> spielen zunehmend eine größere Rolle. Sie ergänzen das Spektrum der Standard-Bauelemente beim Entwurf komplexer Steuerungen. Durch den anwendungsspezifischen Entwurf können maßgeschneiderte Lösungen

<sup>&</sup>lt;sup>24</sup>: Zur Ersteilung und Pflege der eingesetzten Datenbanken waren bisher ca. 6 Mannjahre erfoderlich.

<sup>&</sup>lt;sup>25</sup>: 1. bzw. 2. Semesterarbeit : max. 3 bzw. 4 Monate.

<sup>&</sup>lt;sup>26</sup>: Diplomarbeit : max. 6 Monate.

<sup>27:</sup> auch ASIC genannt (engl. Application Specific Integrated Circuit).

realisiert werden, welche z.B. Vorteile hinsichtlich Geschwindigkeit, Leistungsaufnahme o.ä. Charakteristika aufweisen.

Der Entwurf von ASICs obliegt meist dem Anwender, der i.a. nicht mit der Technik höchstintegrierter Schaltungen<sup>28</sup> vertraut ist. Der Entwickler muß also gute Vorkenntnisse der VLSI-Entwurfstechnik sowie geeignete Werkzeuge besitzen, um diesen Entwurf durchführen zu können. Hierzu wird hinsichtlich einer ausbildungsorientierten Entwicklungsumgebung das VLSI-Entwurfssystem ISIS<sup>29</sup> seit 1987 erfolgreich am Institut eingesetzt [18]. Die leichte Handhabbarkeit des Systems bis hin zur Erstellung der Maskendaten<sup>30</sup> zeigt sich an den erfolgreich gefertigten Entwürfen des Institutes, bei denen u.a. mit zwei ersten Semesterarbeiten innerhalb von drei Monaten ein sehr schneller dual-ported FIFO<sup>31</sup>-Speicher in vollstatischer CMOS<sup>32</sup>-Technologie für den Einsatz in zukünftigen Kommunikationsknoten – und somit für die Lehr- und Forschungsaufgaben des Instituts – entworfen wurde<sup>33</sup>.

Damit ist eine alle wesentlichen Entwurfsschritte umfassende CAD-Entwicklungsumgebung am IND verfügbar.

### Literatur

- [1] Bönsch, W.: "Entwicklung einer MC68000-Adapterkarte am CAD-Entwicklungssystem REDCAD", Semesterarbeit, IND, Universität Stuttgart, 1987.

- [2] Bönsch, W.: "Aufbau und Integration eines automatischen Reflexionsmeßgerätes für LAN-Segmente nach IEEE 802.3", Diplomarbeit, IND, Universität Stuttgart, 1989.

- [3] CADSTAR-SCM, Benutzerhandbuch, Racal-Redac GmbH, München, 1989.

- [4] CADSTAR-PCB, Benutzerhandbuch, Racal-Redac GmbH, München, 1989.

- [5] Denzel, W.: "Untersuchung zu Vermittlungssystemen mit verteilter Steuerung", Dissertationsschrift, Universität Stuttgart, 1987.

- [6] Gihr,O.: "Entwurf und Realisierung der Hardware-Baugruppe für die Erzeugung von Zufallszahlen mit beliebigen Verteilungsfunktionen für den universellen Umweltsimulator UNES", Studienarbeit, IND, Universität Stuttgart, 1984.

- [7] Göldner, E.H.: "Ein Ringsystem mit integrierter Durchschalte- und Paketvermittlung", Dissertationsschrift, Universität Stuttgart, 1988.

- [8] Jahresbericht 1984 1985, IND, Universität Stuttgart. 1985.

<sup>&</sup>lt;sup>28</sup>: auch VLSI genannt (engl.  $\underline{V}$ ery  $\underline{L}$ arge  $\underline{S}$ cale Integration).

<sup>29:</sup> engl. Integrating Systems Into Silicon.

<sup>30:</sup> GDS-II Datenformat.

<sup>31:</sup> engl. First In First Out.

<sup>32:</sup> engl. Complementary Metal Oxid Semiconductor.

<sup>33.</sup> Nachgewiesen durch Tests nach der Fertigung.

- [9] Kauderer, T.: "Datenbankkonsistenz in heterogenen CAD-Systemen", Semesterarbeit, IND, Universität Stuttgart, 1989.

- [10] Lemppenau, W.: "Umweltsimulator für den Funktions- und Lasttest von Nachrichtenvermittlungssystemen", Dissertationsschrift, Universität Stuttgart, 1989.

- [11] LOG/iC, Programmdokumentation, Isdata GmbH, Karlsruhe, 1988.

- [12] LPKF 101 HI-P, Benutzerhandbuch, LPKF GmbH, Hannover, 1989.

- [13] LPKF-Contac, Benutzerhandbuch, LPKF GmbH, Hannover, 1989.

- [14] Moedinger, K.: "CAD-Datentransfer CADSTAR auf VISULA", Semesterarbeit, IND, Universität Stuttgart, 1989.

- [15] Schmidberger, E.: "MC68000-Mikroprozessorkarte mit Doppelbusstruktur", Diplomarbeit, IND, Universität Stuttgart, 1985.

- [16] Schröder, J.: "Hardwareentwicklung am Institut für Nachrichtenvermittlung und Datenverarbeitung", IND, Universität Stuttgart, 1987.

- [17] Schollenberger, W.: "Entwurf und Realisierung einer 32 Bit Rechnerkarte", Diplomarbeit, IND, Universität Stuttgart, 1987.

- [18] Siegel, M., Lemppenau, W.: "Integrierte VLSI-Entwicklungsumgebung für kommunikationsorientierte Schaltkreise", ITG-Fachtagung Mikroelektronik für die Informationstechnik", Stuttgart, 1989.

- [19] Studienführer der Universität Stuttgart, Presseamt der Universität Stuttgart, 1989.

- [20] Tielitz, M.: "Entwurf und Realisierung des Zeitverwaltungs-Moduls des universellen Umweltsimulators UNES", Studienarbeit, IND, Universität Stuttgart, 1984.

- [21] Thurner, T.: "Entwicklung einer Controller-Karte für die Schnittstellen ST506, ESDI und Floppy-Disk für ein 32-Bit Mehrrechnersystem", Diplomarbeit, IND, Universität Stuttgart, 1989.

- [22] VISULA, Benutzerhandbuch, Racal-Redac GmbH, München, 1989.

- [23] Wanders, J.: "Erstellung einer Datenbank für den rechnerunterstützten Schaltungsentwurf", Studienarbeit, IND, Universität Stuttgart, 1986.

- [24] Weiß, W.: "Über Struktur, Betriebsweise und Verkehrsleistung eines diensteintegrierten Vermittlungssystems für Fernsprech- und Datenverkehr", Dissertationsschrift, Universität Stuttgart, 1984.

- [25] Willi, H.J.: "Anpassung der REDAC-Bibliotheken an den Standard IEEE 91", Studienarbeit, IND, Universität Stuttgart, 1987.

- [26] Winter, P.: "Entwurf eines Interface-Moduls für den Anschluß des Umweltsimulators UNES an eine Nebenstellenanlage", Studienarbeit, IND, Universität Stuttgart, 1985.