## INSTITUT FÜR KOMMUNIKATIONSNETZE UND RECHNERSYSTEME

Prof. Dr.-Ing. Andreas Kirstädter

## **Copyright Notice**

© 1996 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder.

Institute of Communication Networks and Computer Engineering

University of Stuttgart

Pfaffenwaldring 47, D-70569 Stuttgart, Germany

Phone: ++49-711-685-68026, Fax: ++49-711-685-67983

Email: mail@ikr.uni-stuttgart.de, http://www.ikr.uni-stuttgart.de

## A New MAC Protocol For High-Speed Multimedia ATM LANs

### Martin Götzer

University of Stuttgart

Institute of Communications Switching and Data Technics

Seidenstraße 36

D-70174 Stuttgart

email: goetzer@ind.uni-stuttgart.de

### **Abstract**

Protocols for shared media Local Area Networks (LAN) are optimized for high asynchronous traffic throughput. Multimedia applications, e.g. interactive video, require low traffic delay with low delay jitter. Peak bit rate reservation for this kind of traffic guarantees the required quality of service but usually results in a waste of bandwidth due to the very bursty traffic produced by multimedia applications.

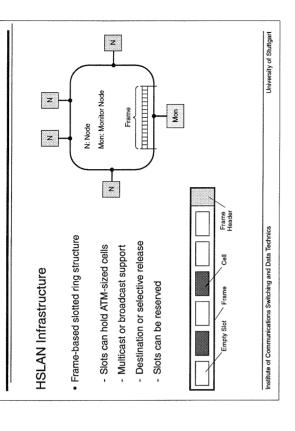

In this paper, a new MAC protocol is presented which integrates isochronous and asynchronous traffic in a ring LAN. Slots which each can hold an ATM cell are placed in fixed-length frames. In the isochronous traffic class, a monitor node grants access to slots which are determined by their position in every frame to requesting nodes. Thus for isochronous traffic channels the protocol provides guaranteed bandwidth with guaranteed maximum ATM cell delay. In the new approach asynchronous traffic can use the unallocated and, in addition, all the reserved slots that are currently not used within isochronous connections. It is no waste of bandwidth to reserve an isochronous channel with its peak bandwidth for a bursty connection because the bandwidth not used by the connection can be used for asynchronous traffic.

Each node has a list of "usable slots in frame" to determine which slots in every frame are currently reserved for this node. The node "owns" these slots, i. e. it decides how the slots are to be used. In any case they can be used for the node's own isochronous traffic, and the node can decide whether the slot can be used for asynchronous traffic within the next ring cycle by setting the Available bit in the slot header. Incoming asynchronous cells are stored in the node's insertion buffer. Unreserved slots are always available for asynchronous traffic.

To avoid an insertion buffer overflow in case of heavy asynchronous traffic, an available counter is introduced. This counter's value represents the sum of all the node's slots that are marked as "available" on the ring, in addition to the number of cells in the insertion buffer. If the available counter reaches a limit which is at a maximum the number of cells the insertion buffer can hold, the node's outgoing slots are marked as unavailable, i. e. the Available bit is not set. Slots with the Available bit not set must not be used for asynchronous cells. This mechanism ensures that the insertion buffer cannot overflow.

On top of this basic medium access mechanism, a credit-based access algorithm for the asynchronous traffic is engaged in order to achieve fairness. The reset interval in this algorithm may be comparably long because all timing critical traffic will be sent over isochronous channels, leading to a high overall ATC throughput.

## A New MAC Protocol For High-Speed Multimedia ATM LANs

Introduction

## Martin Götzer

Institute of Communications Switching and Data Technics University of Stuttgart Outline

Introduction - Motivation

- HSLAN architecture

- Isochronous traffic integration

New MAC protocol

- Mechanisms

- Node structure

- Fairness protocol

Simulation Results

Conclusion

Institute of Communications Switching and Data Technics

University of Stuttgart

## How can isochronous traffic be integrated?

Introduction

- The standard ATM approach:

- Give high priority to the isochronous traffic class

- Introduce artificial delay in order to recover from high cell delay jitter

- Hope the user doesn't realize cell losses

- The reservation approach:

- Reserve the peak bandwidth to minimize end-to-end delay

- Waste reserved but currently unused bandwidth

- The new approach:

- Reserve the peak bandwidth in a frame-based slotted ring

- Allow asynchronous cells to use reserved but currently unused slots

Institute of Communications Switching and Data Technics Univer-

## New MAC Protocol

- Isochronous channel reservation

- Request peak bandwidth

- Get a list of slots to be used in every frame

- "Own" these slots

- Insertion buffer

- All asynchronous traffic goes through the insertion buffer

- All isochronous traffic passes the insertion buffer ightarrow low delay

- Own (reserved) slots

- Can be used for isochronous cells even if they are busy

- Busy slot content is transferred to the insertion buffer

- ightarrow In case of heavy load the insertion buffer could overflow

Institute of Communications Switching and Data Technics

University of Stuttgart

## New MAC Protocol

Available bit

- Can be set by a node in its "own" (reserved) slots

- Allows other nodes to use the node's slots for asynchronous traffic

- Can be unset in order to guarantee the "own" slot to be left free from asynchronous traffic during round-trip

- Available counter

- Counter value = number of slots that are marked "available"

- + number of cells in the insertion buffer

- Counter limit = number of cells the insertion buffer can hold

- Prevents the insertion buffer from overflow

Institute of Communications Switching and Data Technics

University of Stuttgart

# Node Structure Receive Buffer Buffer Buffer Saying Cell Treatment In France In France

- Credit mechanism:

- Each node gets an initial amount of credits each cycle

- A credit is the permission to use one free, available slot

- To send a cell from the insertion buffer, no credit is needed

- A node is active as long as it is enabled or its insertion buffer is not empty

- A new cycle begins if there is no active node left

Institute of Communications Switching and Data Technics

University of Stuttgart

| Slot/C  | Slot/Cell Format                           | ACF Format                                                                                                                                                                        |

|---------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 2 3   | 3 4 5 6 7 8<br>ACF                         | Busy/ Available Active Reset Sym/ Packet EOP Mon                                                                                                                                  |

| 1 E 4 N | VCI<br>PT, Res<br>HEC                      |                                                                                                                                                                                   |

| 66      | Payload                                    | Active Node = This bit is set by an active node and reset by the monitor node Reset = 1: Reset op interment issued by the monitor node 0: No Reset SynAksyn = 1: STC nell content |

| ACF.    | Access Control Field                       |                                                                                                                                                                                   |

| VCI:    | Virtual Channel Identifier<br>Payload Type | EUF = 1: Last cell of packet  O: Not last cell of packet  Monitor bit                                                                                                             |

| Res.:   | Reserved                                   |                                                                                                                                                                                   |

| HEC: 1  | Header Error Check                         |                                                                                                                                                                                   |

| C Load 10                                        | - Simulation: 16 nodes, each node sends same amount of data to all other nodes - Reserved: 128 out of 256 slots for ITC channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - Ring bandwidth = 2048 kCells/s, 384 bits/Cell (786 Mbps) - Conventional Reservation: ATC cannot use reserved slots | University of Stuttgart                                 |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Simulation Results: ATC Throughput Over ITC Load |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Simulation Result Upper Bound Conventional Reservation 0 500.0 1000.0 1500.0 2000.0 Offered ITC load in KCells/s     | Institute of Communications Switching and Data Technics |

| Simula                                           | e/sells/s in troping the Model of the Model | 10 OTA                                                                                                               | Institute of Cor                                        |

| New method for isochronous traffic integration in LANs Peak bitrate reservation without waste of bandwidth Seamless Multimedia integration Implementation: Standard programmable logic 32-bit data path @ 30 MHz 960 Mbps link bit rate 2 Mcells/s, 125µs frame duration - 256 reservable isochronous channels with 3 Mbps each                                                                                           | Conclusion                                                                 | 11                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------|

| <ul> <li>New method for isochronous traffic integration in LANs</li> <li>Peak bitrate reservation without waste of bandwidth</li> <li>Seamless Multimedia integration</li> <li>Implementation:</li> <li>Standard programmable logic</li> <li>32-bit data path @ 30 MHz</li> <li>960 Mbps link bit rate</li> <li>2 Mcells/s, 125µs frame duration</li> <li>256 reservable isochronous channels with 3 Mbps each</li> </ul> |                                                                            |                       |

| Peak bitrate reservation without waste of bandwidth     Seamless Multimedia integration     Implementation:     Standard programmable logic     32-bit data path @ 30 MHz     960 Mbps link bit rate     2 Mcells/s, 125µs frame duration     256 reservable isochronous channels with 3 Mbps each                                                                                                                        | <ul> <li>New method for isochronous traffic integration in LANs</li> </ul> |                       |

| Seamless Multimedia integration     Implementation:     Standard programmable logic     32-bit data path @ 30 MHz     960 Mbps link bit rate     2 Mcells/s, 125µs frame duration     256 reservable isochronous channels with 3 Mbps each                                                                                                                                                                                | <ul> <li>Peak bitrate reservation without waste of bandwidth</li> </ul>    |                       |

| Implementation:     Standard programmable logic     32-bit data path @ 30 MHz     960 Mbps link bit rate     2 Mcells/s, 125µs frame duration     256 reservable isochronous channels with 3 Mbps each                                                                                                                                                                                                                    | <ul> <li>Seamless Multimedia integration</li> </ul>                        |                       |

| <ul> <li>Standard programmable logic</li> <li>32-bit data path @ 30 MHz</li> <li>960 Mbps link bit rate</li> <li>2 Mcells/s, 125µs frame duration</li> <li>256 reservable isochronous channels with 3 Mbps each</li> </ul>                                                                                                                                                                                                | • Implementation:                                                          |                       |

| <ul> <li>- 32-bit data path @ 30 MHz</li> <li>- 960 Mbps link bit rate</li> <li>- 2 Mcells/s, 125µs frame duration</li> <li>- 256 reservable isochronous channels with 3 Mbps each</li> </ul>                                                                                                                                                                                                                             | - Standard programmable logic                                              |                       |

| - 960 Mbps link bit rate<br>- 2 Mcells/s, 125µs frame duration<br>- 256 reservable isochronous channels with 3 Mbps each                                                                                                                                                                                                                                                                                                  | - 32-bit data path @ 30 MHz                                                |                       |

| - 2 Mcells/s, 125µs frame duration<br>- 256 reservable isochronous channels with 3 Mbps each                                                                                                                                                                                                                                                                                                                              | - 960 Mbps link bit rate                                                   |                       |

| - 256 reservable isochronous channels with 3 Mbps each                                                                                                                                                                                                                                                                                                                                                                    | - 2 Mcells/s, 125μs frame duration                                         |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                           | - 256 reservable isochronous channels with 3 Mbps each                     |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                           | Institute of Communications Switching and Data Tachnics                    | Honoreity of Stuffger |